Home > Servers > Rack and Tower Servers > Intel > White Papers > Memory Population Rules for Intel® Xeon® Scalable Processors on PowerEdge Servers > Memory topography and terminology

Memory topography and terminology

-

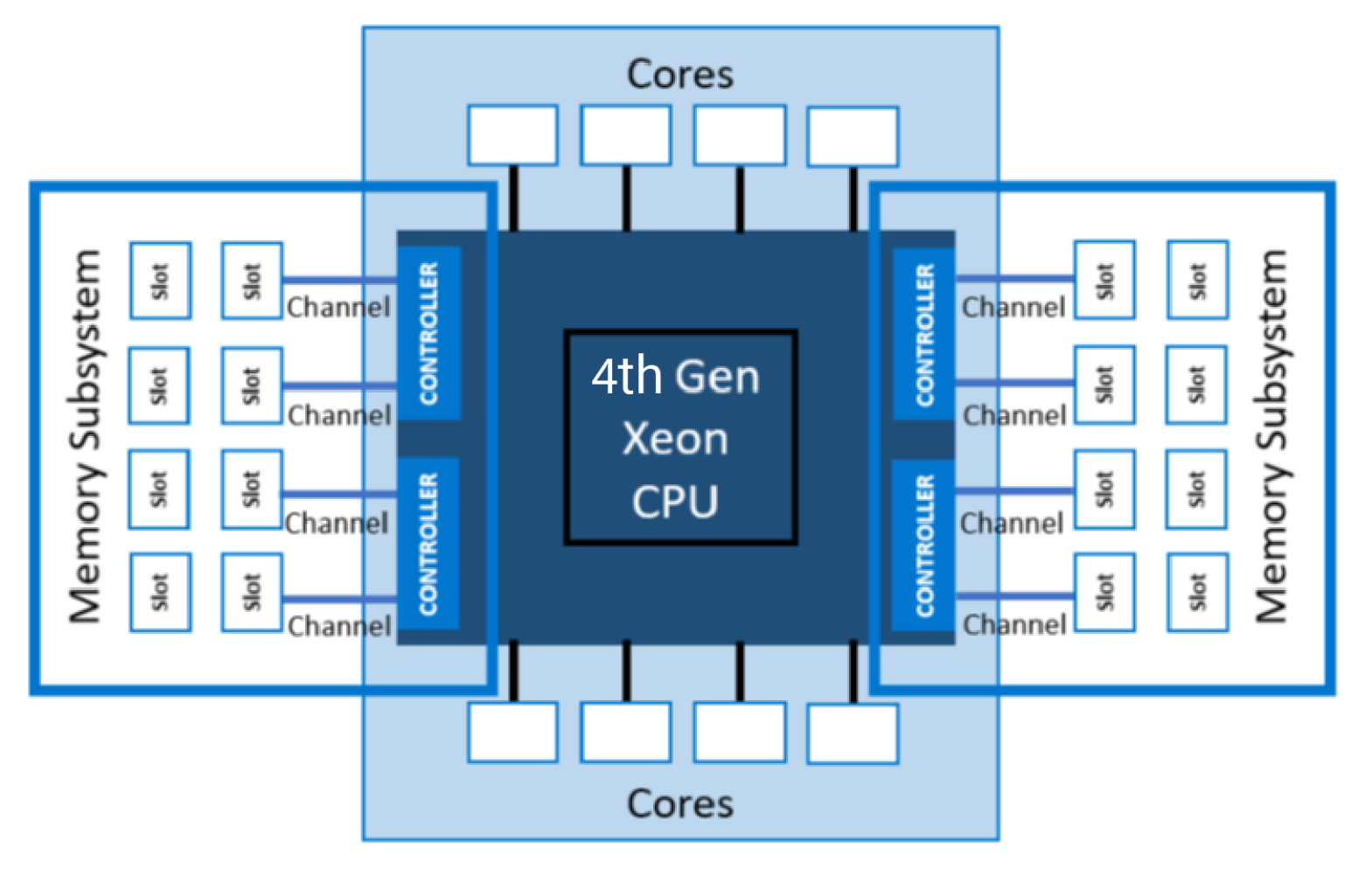

Figure 1. Overview of the CPU-to-memory subsystem connectivity

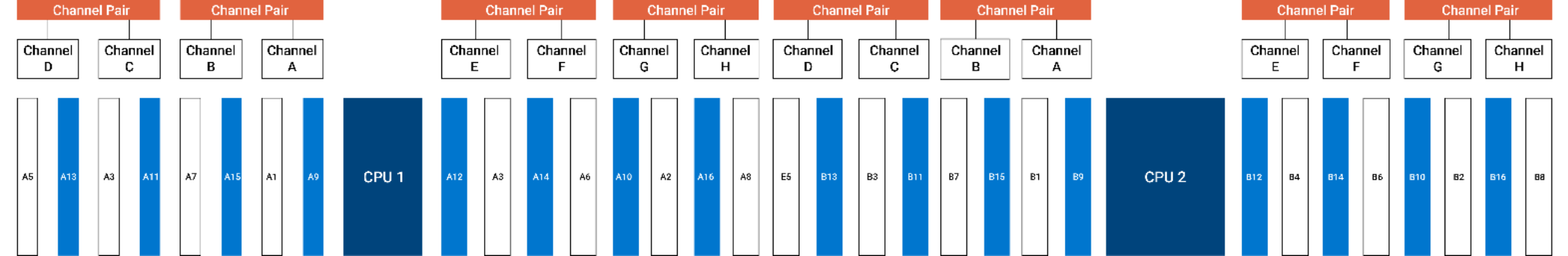

Figure 2. Decoding DIMM lettering/numbering to Channel lettering/numbering (2 CPUs)

To understand the relationship between the CPU and memory, terminology illustrated in Figure 1 must first be addressed:

- Memory controllers are digital circuits that manage the flow of data going from the computer’s main memory to the corresponding memory channels. Each controller was intended to be populated with at least one DIMM. Xeon® processors have four memory controllers.

Memory channels are the physical layer on which the data travels between the CPU and memory modules. Channels were intended to be populated in a symmetrical fashion, so that when two channels horizontal to one another are populated, an interleave set will be created. Xeon® processors have eight memory channels.

Processor

Channel

AChannel

BChannel

CChannel

DChannel

EChannel

FChannel

GChannel

HSlots for Processor 1:

A1 and A9

A7 and A15

A3 and A11

A5 and A13

A4 and A12

A6 and A14

A2 and A10

A8 andA16

Slots for Processor 2:

B1 and B9

B7 and B15

B3 and B11

B5 and B13

B4 and B12

B6 and B14

B2 and B10

B8 and B16

Figure 3. Memory Channels

- Memory slots host individual memory modules, such as DIMMs or DCPMMs. Xeon® processors have two slots per channel, so there are a total of sixteen slots per CPU for memory module population. As seen in Figure 2, for CPU1, DIMM 0 slots A1-A8 (the white slots) are the first eight memory modules to be populated, while DIMM 1 slots A9-A16 (the blue slots) are the last eight to be populated. Similarly, for CPU2, DIMM 0 slots B1-B8 (the white slots) are the first eight memory modules to be populated, while DIMM 1 slots B9-B16 (the blue slots) are the last eight to be populated. See also the DIMM slot/channel numbering in Figure 3.

- The memory subsystem is the combination of all the independent memory functions listed above.

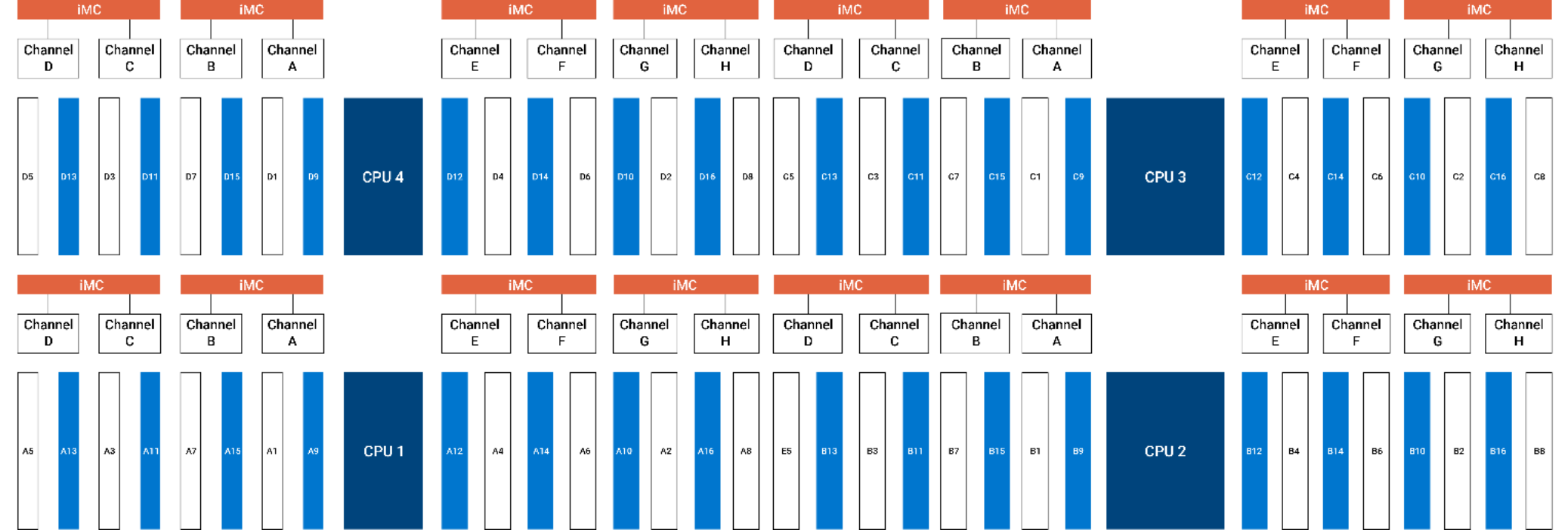

Figure 4. Decoding DIMM lettering/numbering to Channel lettering/numbering (4 CPUs)

For this quad CPU design, populate the memory in round robin order, starting with CPU1, then CPU2, CPU3 and CPU4. Optimized population order is:

A1,B1,C1,D1,A2,B2,C2,D2,A3,B3,C3,D3, and so on.