Home > Servers > Rack and Tower Servers > Intel > White Papers > Memory Population Rules for Intel® Xeon® Scalable Processors on PowerEdge Servers > Memory channel population

Memory channel population

-

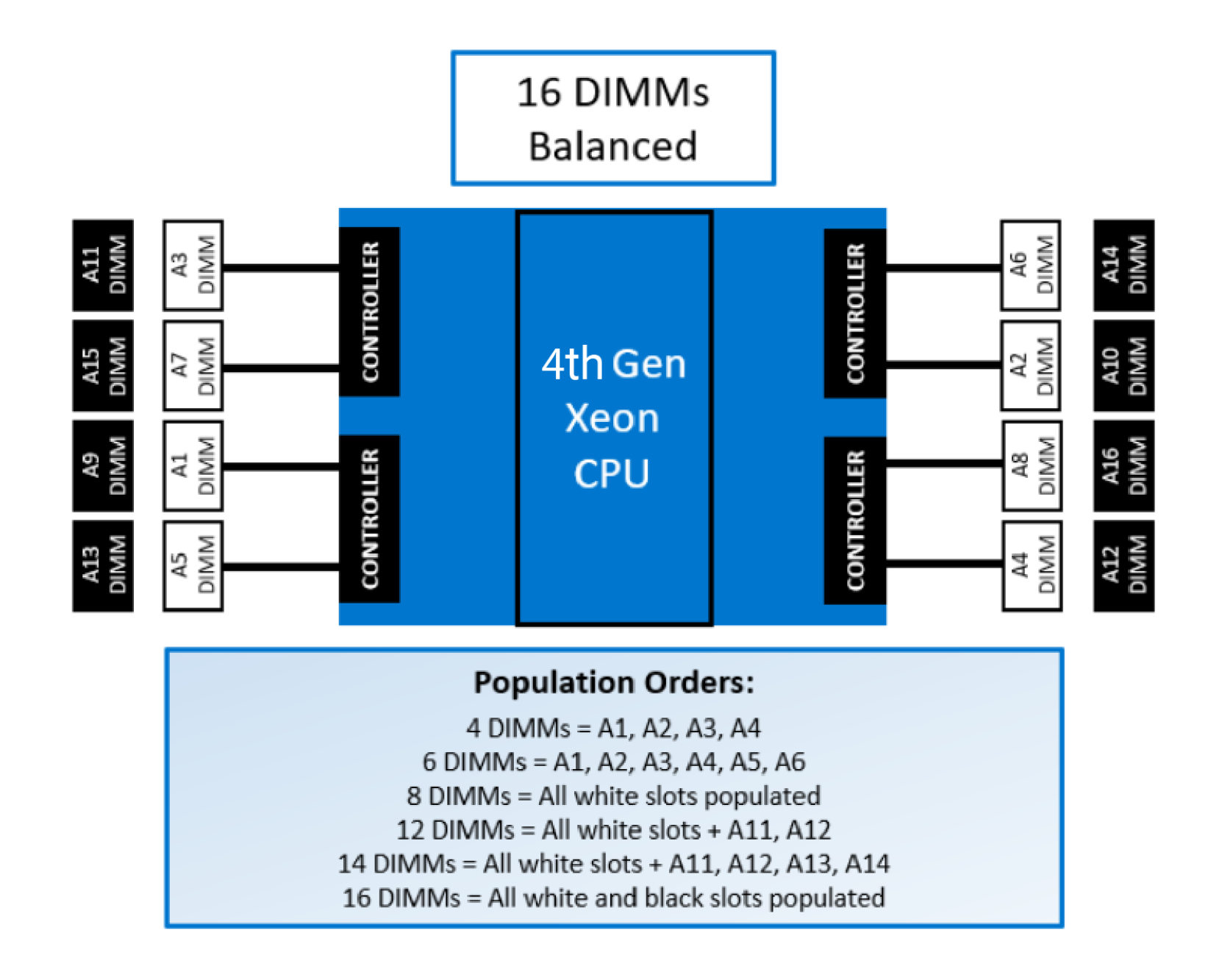

To achieve a balanced configuration, populate either eight or sixteen DIMMs per CPU. By loading each channel with one or two DIMMs, the configuration is balanced and has data traveling across channels most efficiently on one interleave set. Following this guideline yields the highest memory bandwidth and the lowest memory latency.

If a balanced configuration of sixteen or eight DIMMs per CPU is not possible, the next best option is a near balanced configuration. To obtain a near balanced configuration, populate four, six, twelve or fourteen DIMMs per CPU in a symmetrical fashion. When any number of DIMMs other than four, six, twelve or fourteen is populated, disjointed memory regions are created which introduce more interleave sets.

Figure 6. DIMM population order for balanced and near balanced configurations

The last guideline is that DIMMs must be populated in an assembly order because Xeon® processors have a symmetrical architecture for each type of CPU core count. Figure 5 illustrates the assembly order in which individual DIMMs should be populated, starting with A1 and ending with A16. Figure 5 is reflective of 1 CPU configurations; for CPU2 configurations, populate respective DIMMs on CPU2 (B1-B16).