Example B: Data availability and protection in semiconductor design

Home > Storage > PowerScale (Isilon) > Product Documentation > Management and Migration > Storage Tiering with Dell PowerScale SmartPools > Example B: Data availability and protection in semiconductor design

Example B: Data availability and protection in semiconductor design

-

Logical and physical design and verification are complex early stages in the electronic design automation (EDA) process for semiconductor production. This design data is critical. Time-to-market is paramount in this industry. The company is counting on the revenue from this product, and the workflow is high priority. Multiple engineers from around the globe will typically be collaborating on the project, and all require timely access to the data.

Design data and other intellectual property are often reused in subsequent projects, so archive and retention requirements spanning decades are commonplace. Moreover, it can remain critical for many years, even decades. But it is not timely—nobody has to access older designs at high-performance speeds. All instances in which historical design data is referenced are not time-critical enough to change the type of disk they are stored on. However, an argument could be made against deep archive in legal discovery timeframes. Older designs are critical, but not timely.

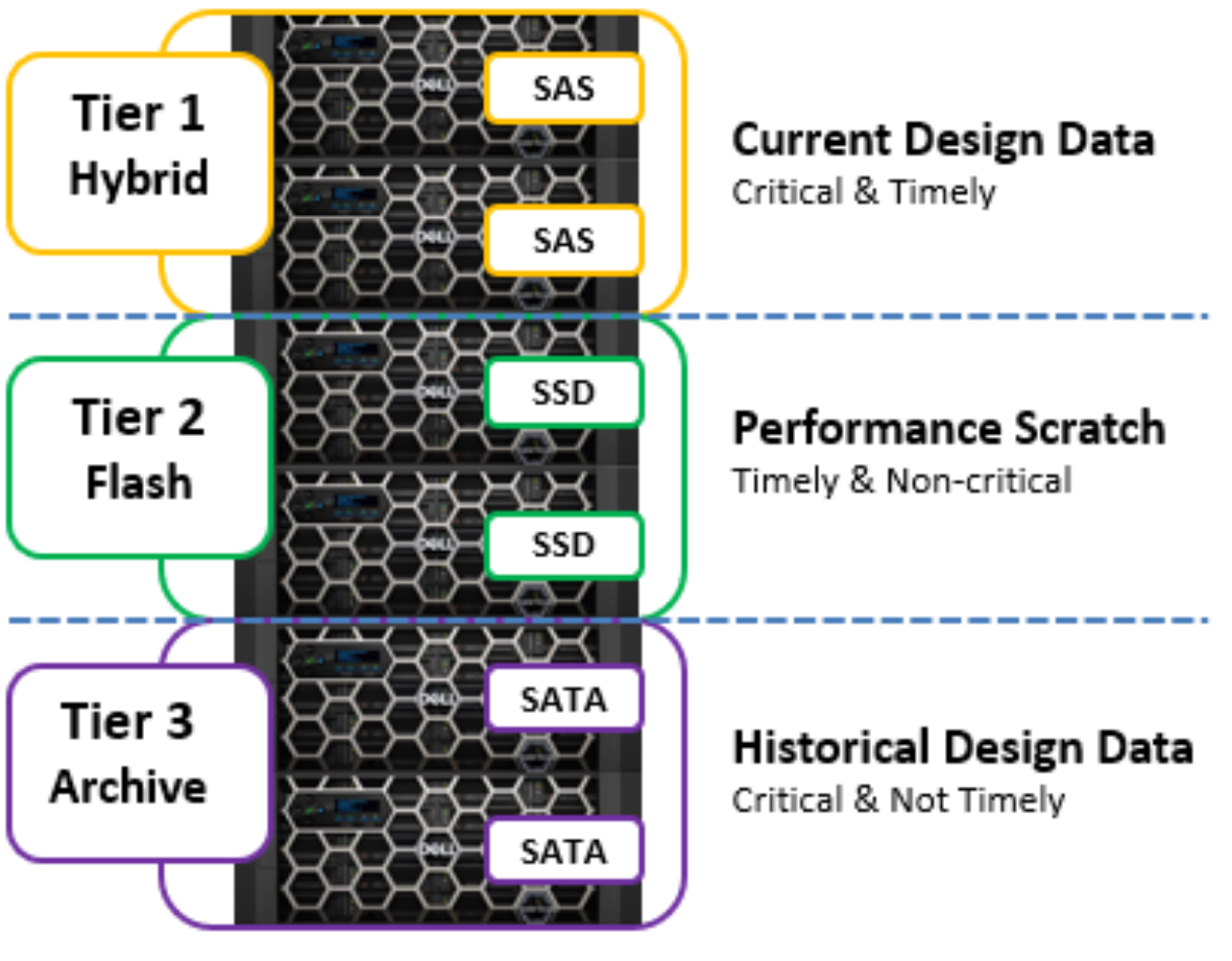

Figure 25. Data performance and protection in EDA

EDA workflows often employ an additional tier of storage, or scratch space, for the transient processing requirements of HPC compute farms. Typically, this scratch space has high transactional performance requirements and often employs an SSD-based storage node. However, because scratch is temporary data, the protection and retention requirements are low.

Using SmartPools, these requirements can be met with a three-tier architecture using high-performance SAS and SSD nodes for both the performance and scratch tiers. The architecture will use high-capacity SATA for the high-capacity archive tier. One file pool policy would restrict historical design data to the high-capacity tier, protecting it at a high level. Another would restrict current design data to the fastest tier at the same protection level.